根据韩媒ZDNet Korea的报道,固态技术协会JEDEC有望放宽对HBM4内存的高度限制,这将对内存行业带来一定的影响。内存厂商将不再被迫转向混合键合技术,这一调整有望为内存行业的发展带来新的机遇。

HBM内存技术背景

作为对DRAM进行3D堆叠的产品,HBM内存的z轴封装高度限制对其性能和应用有着重要的影响。目前,HBM内存最大的DRAM堆叠层数为12层,允许的最大厚度为720微米。

当前技术路线

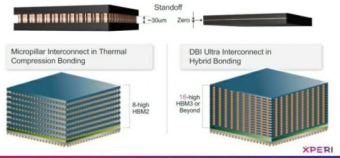

在3D堆叠技术方面,目前主要的两家内存厂商SK海力士和三星电子采用了不同的工艺路线。SK海力士采用了MR-RUF工艺,而三星电子则使用了TC NCF路线。不过,两者共同之处在于使用凸块实现层层连接。

HBM3E 12H产品

三星电子最近推出的HBM3E 12H产品上,通过对NCF材料的优化,芯片之间的间隙已经降低至7微米,展示出了技术的进步和创新。

HBM4内存的挑战

未来,HBM4内存将提升至最多16层。然而,在DRAM芯片本身的总厚度进一步提升的情况下,凸块厚度开销成为了一个重要的问题。传统技术可能无法实现16层DRAM的堆叠。

混合键合技术

混合键合技术无需凸块,可以使各DRAM层间更加紧密,从而降低DRAM堆叠的高度。然而,这种技术相对于传统方案而言成本较高,且尚未成熟,因此内存厂商尽可能地避免使用。

JEDEC的调整

据报道,JEDEC主要参与方已同意将HBM4的高度限制放宽至775微米,这将为内存厂商提供更多的发展空间,并为混合键合HBM内存的商业化留出更多时间。

JEDEC有望放宽HBM4内存高度限制,这一调整将为内存行业带来新的机遇和挑战。内存厂商将在这一新的技术背景下展开更加激烈的竞争,推动行业的持续发展。